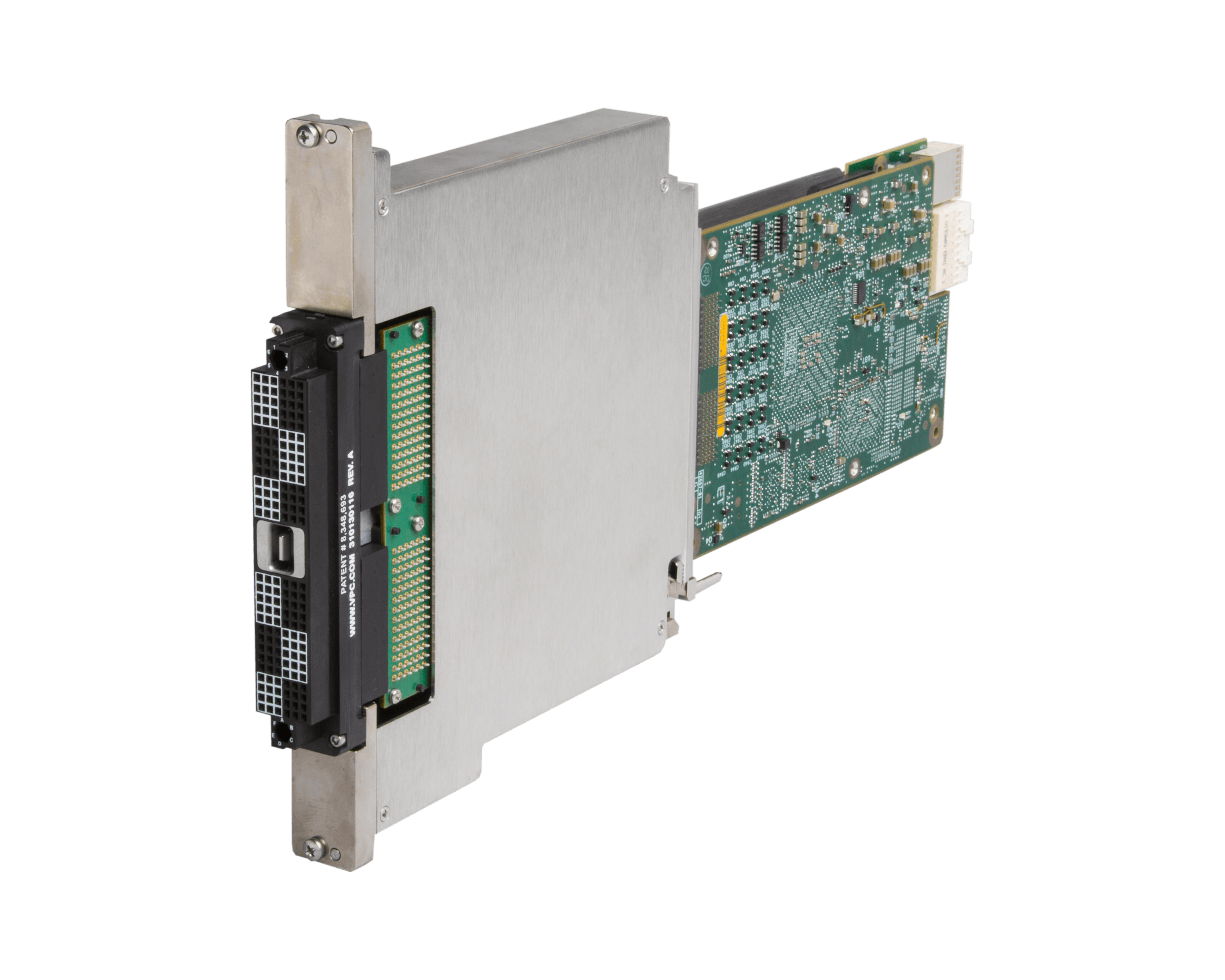

eDigital-6020A

Digital Test Instrument

High Pin Count TTL/LVTTL/LVDS with FPGA Configurability and VPC Funnel Best choice when current or future requirements include:

- High pin count TTL/LVTTL capability

- High throughput IEEE 1149.1 test and memory programming

- Conventional stored pattern capability

- FPGA configurability to address a variety of low-level bus specifications

- Integrated Instrument and Virginia Panel Funnel Interface

- Single-piece instrument and funnel assembly with QuadraPaddle interface module

- Supports both i2 MX cables and G20 ITAs

- 3.3V LVTTL is TTL-Tolerant and compatible

- Supports up to 64 LVTTL I/O pins, or 32 LVDS differential pairs

- Broad IEEE 1149.1 Boundary Scan support

- Supported by the runtime software from the major third-party vendors

- Conventional interconnect tests through large-capacity Flash programming

- Multiple Test Access Ports and large pin count parallel I/O

- Serial Vector Format (SVF) runtime capability (HSSub App included in TriFlex software)

- Teradyne eDigital HSSub App provides conventional stored pattern (truth table) testing (included in HSSub TriFlex software)

- Flexible low-level HSSub Tier 1 I/O Bus Processing

- Reconfigurable HSSub Tier 1 (I/O Bus Processing) of the HSSub Three Tier Architecture implemented by a large Test Defined FPGA and local memory

- Configured in seconds by HSSub Apps supported by Teradyne, end-users, and third-party developers

- HSSub App development, if required, is simplified by FPGA template code based on standard design patterns

- HSSub TriFlex Infrastructure Software interfaces provide access to the hardware from Windows Tier 3 or HSSub Tier 2 instruments